# 3D integrated system for advanced intelligent computing

Ram Eknath Munde, Noah Vaillancourt, Heng-Ray Chuang, Chongke Gu, Yifan Wang & Raisul Islam

**To cite this article:** Ram Eknath Munde, Noah Vaillancourt, Heng-Ray Chuang, Chongke Gu, Yifan Wang & Raisul Islam (2025) 3D integrated system for advanced intelligent computing, *Advances in Physics: X*, 10:1, 2599301, DOI: [10.1080/23746149.2025.2599301](https://doi.org/10.1080/23746149.2025.2599301)

**To link to this article:** <https://doi.org/10.1080/23746149.2025.2599301>

© 2025 The Author(s). Published by Informa UK Limited, trading as Taylor & Francis Group.

Published online: 15 Dec 2025.

Submit your article to this journal

View related articles

View Crossmark data

REVIEW ARTICLE

OPEN ACCESS

## 3D integrated system for advanced intelligent computing

Ram Eknath Munde<sup>a</sup> , Noah Vaillancourt<sup>a</sup>, Heng-Ray Chuang<sup>a</sup>, Chongke Gu<sup>b</sup>, Yifan Wang<sup>b</sup> and Raisul Islam<sup>a,b</sup>

<sup>a</sup>School of Materials Engineering, Purdue University, West Lafayette, IN, USA; <sup>b</sup>Elmore Family School of Electrical and Computer Engineering, Purdue University, West Lafayette, IN, USA

### ABSTRACT

Emerging technologies such as artificial intelligence (AI), large-scale molecular simulations, and next-generation materials and drug discovery demand unprecedented computational power and high-bandwidth interconnects. Conventional two-dimensional integrated circuits (2D ICs) are nearing their physical and performance limits due to challenges in thermal management, signal integrity, and leakage currents. Three-dimensional integrated circuits (3D ICs) offer a promising pathway to overcome these limitations by vertically stacking multiple device layers, thereby reducing interconnect lengths and enabling a broad range of high-performance applications. This paper presents a comprehensive review of 3D ICs systems, with an emphasis on energy efficiency across various conventional and heterogeneous integration schemes, packaging architectures, and the trade-offs between thermal and electrical performance. We examine the relative merits of different bonding techniques, floorplanning algorithms, cooling solutions, and power delivery network (PDN) designs, highlighting their interdependencies and optimization challenges. The insights presented in this review are intended to help researchers and designers identify and implement strategies that enhance the performance, energy efficiency, and reliability of 3D ICs for high-performance computing applications.

### ARTICLE HISTORY

Received 9 August 2025

Accepted 25 November 2025

### KEYWORDS

Advanced packaging; 3D integrated circuits (3D ICs); intelligent computing; heterogeneous integration; thermal management; artificial intelligence; oxide semiconductors; hybrid bonding; through silicon vias; power delivery networks; signal integrity

## 1 Introduction

Microprocessor technology has seen great development since its inception in the 1960s. The primary driving force behind this advancement has been the scaling of silicon (Si) metal-oxide-semiconductor field-effect transistors (MOSFETs), which has enabled transistor dimensions to shrink from several millimetres to just a few nanometres. Moore's law has been the guiding beacon for this enormous progress in scaling, which stated that the number of transistors doubles approximately every two years [1]. While Moore's law did not mention anything about the physical scaling of the transistors, the doubling of the number of transistors was guided by Dennard scaling, which stated that as transistors scale, their clock frequency increases while power consumption remains constant [2,3]. Unfortunately, this scaling lasted until 2005-2006, since when clock frequency stopped increasing because of high dynamic energy that scales as the square of clock frequency [4]. Subsequently, architectural scaling emerged through the introduction of multi-core modules within the chip [5]. The impact of this trend on human life has been nothing short of remarkable. However, like every trend, this scaling approach is reaching its limits. Packaging limitations, particularly lithographic constraints, have become more pronounced in recent years, making it extremely difficult to pack more transistors at the nanoscale. Even advanced lithographic techniques have become prohibitively expensive for most fabrication facilities, leaving only a few competitive fabs remaining in the market [6-8]. Furthermore, the scaling of physical dimensions of the device comes at a cost of interconnect delay, reduced signal integrity, and heat dissipation issues to the extent that these bottlenecks hinder the growth of two-dimensional integrated circuits (2D ICs). With the advent of artificial intelligence (AI) models experiencing a 10 $\times$  increase in the number of parameters per year, and the growing requirements for high performance with low power consumption, today's multi-core 2D IC architecture has been driven to its physical and economic limits. Therefore, the use of the third dimension for scaling is inevitable [9-12].

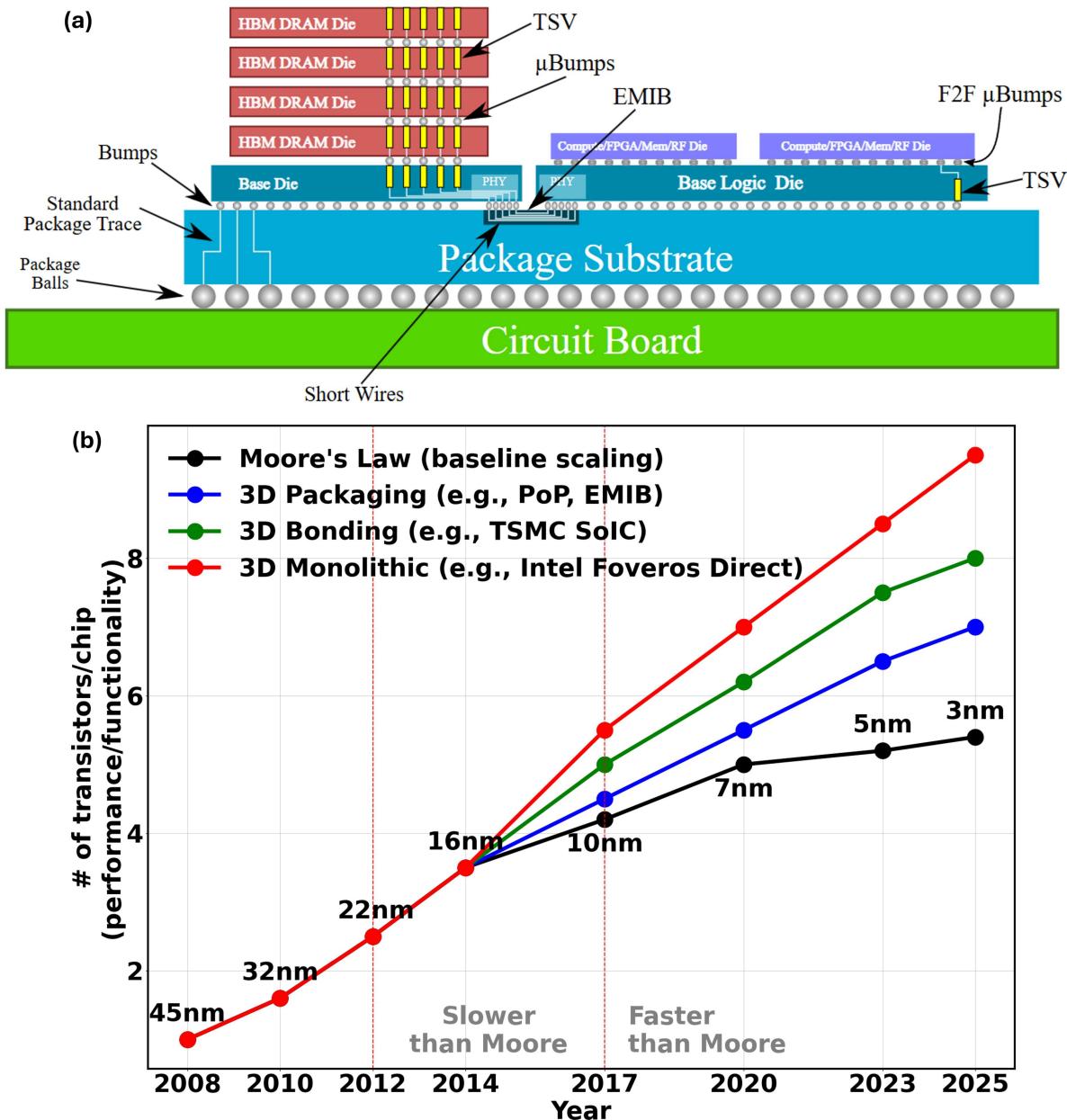

Three-dimensional integrated circuits (3D ICs) offer efficient scaling by harnessing the vertical dimension for stacking multiple active die layers interconnected through high-density vias or Cu-Cu die bonding. This approach significantly improves computing performance by reducing total interconnect length, signal delay, and footprint. 3D ICs provide improved memory bandwidth by allowing the stacking of multiple primary or cache memory units, resulting in the increase of the available memory capacity [13,14]. Early research results have demonstrated the transformative potential of 3D ICs in alleviating interconnect bottlenecks and supporting the development of advanced system-on-chip (SoC) architectures [15-17]. Recognising this trend, there has been increased interest in adopting 3D design in dynamic random-access memory (DRAM), in the form of high bandwidth memory (HBM), which has been industrially adopted by companies like Micron and SK Hynix since 2015 [18] to handle the AI training load in datacenters. State-of-the-art advancements in 3D IC technology, such as AMD's 3D V-Cache, TSMC's SoIC and Intel's Foveros architectures (see Figure 1a), demonstrate the commercial viability of advanced stacking technology [19-22]. With 3D integration, Moore's original law is not obsolete; rather, it has gained an additional dimension as depicted in Figure 1b. However, this added dimension brings both opportunities and challenges. This paper discusses these challenges and examines important emerging trends in 3D ICs technology.

## 2 Intelligent computing driven by 3D integrated systems

The acceleration of the discovery and creation of knowledge in recent history can be largely attributed to the accessory intelligence obtained through the advancement of artificial intelligence (AI) enabled by microelectronics. Initially, massively improved communication and computational aid enabled by a predominantly man-focused relationship with machines stimulated this growth. The power of this collaboration drove rapid innovation of machines, both in software and hardware forms. This innovation has pushed the boundaries of intelligent systems to incredible horizons. For instance, In 2016, the inflection point came when AlphaGo, an AI computer programme by DeepMind, defeated Lee Sedol, the top human Go master [23].

The growth of intelligent computing began with feature scaling, underwent the era of 2D, multicore expansion, and has begun vertical aggregation in response to the physical and economic limitations. Planar architecture is hindered by the inherent complications of making off-chip interconnectivity [24]. As AI is applied to emerging landscapes with evolving requirements for processing speed, data storage, and energy

**Figure 1.** (a) Foveros is a high-performance 3D IC face-to-face (F2F) based packaging technology designed by Intel [19]. (b) 3D ICs Performance with different node technologies (reproduced with permission from [20]).

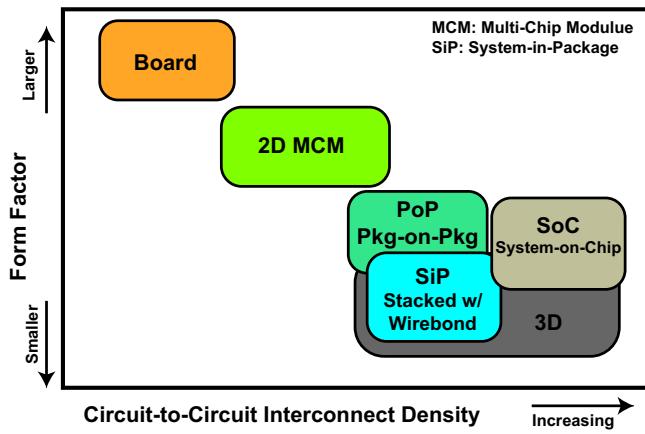

efficiency, inefficiencies resulting from the need of increasing off-chip communication (termed as Von Neumann bottleneck) is going to be unsustainable in the near future [25]. Instead, system-level optimisation of the full computing stack drives 3D integration by increasing interconnect density, minimising power dissipation, and improving memory bandwidth, thus providing high-capacity, low-cost opportunities for the future (Figure 2) [24,26].

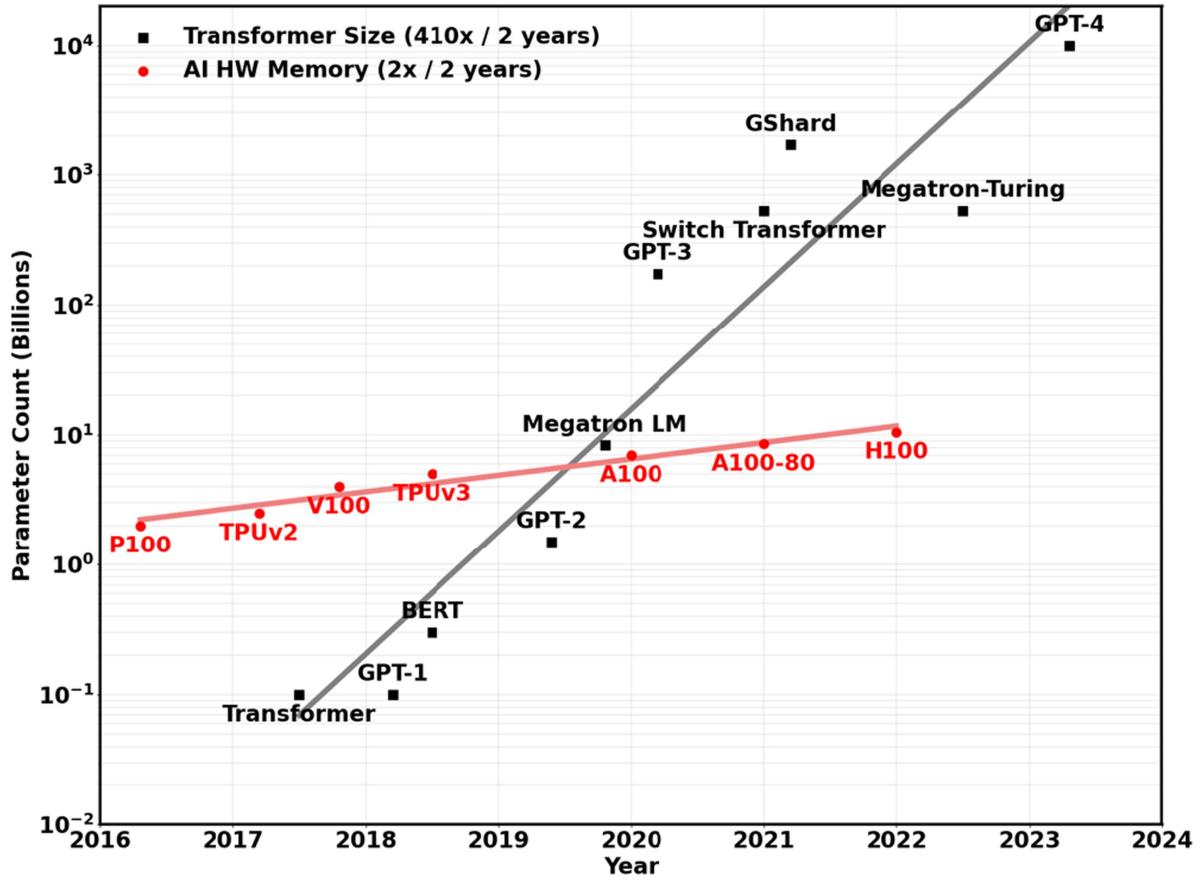

For training an intelligent computational model requires significant investment in both energy and money, owing to the introduction of Kaplan scaling, which asserts that performance improvements are a result of an increase in the number of parameters an AI solution utilises [27]. Scaling the number of parameters is enabled by chips having fast access to memory which stores the massive datasets required for training. 3D integration poses a solution to the bottlenecks of off-chip memory by improving the memory bandwidth with vertical stacking and increasing interconnect density. To further the abilities of intelligent computing, 3D integration also provides benefits through the heterogeneous integration (HI) of

**Figure 2.** Form factor and interconnect density improvements of various packaging technologies (reproduced with permission from [24]).

technologies. HI means packaging chips of different functionalities, feature sizes, and even fabricated in different fabs into a single unified system to improve performance. This modularity of design speeds up commercialisation, reduces cost, and eases IP challenges [28]. The ability to combine technologies on single chips through 3D integration provides better coordination of storage, communication, and computation to accelerate the development of intelligent computing and large scale AI models (Figure 3) [23,29].

### 3 Packaging of 3D ICs

Packaging and assembly are key building blocks of any commercial technology. Several approaches are adopted for the packaging of 3D ICs, including monolithic 3D integration, direct oxide wafer bonding, metal bonding using through-silicon-vias (TSVs) and recently developed self-assembly based integration [20]. Table 1 provides a comparative analysis of 2D, 2.5D, and 3D packaging solutions. In the process of monolithic integration, devices are connected by interlayer vias and stacked on the same wafer. The vias in monolithic 3D integration are fine, which avoids the application of a keep-out zone and reduces the concern of induced mechanical stress [30]. However, the device stacking sequence in monolithic 3D integration is limited to thermal budgets. To prevent damaging the bottom layers, the devices on the top layers must have a lower thermal budget. In recent studies of monolithic 3D integration, two-dimensional semiconductors [31,32] and oxide semiconductors such as indium-gallium-zinc-oxide (IGZO) and indium-tin-zinc-oxide (ITZO) [33,34] have shown potential due to their lower processing temperatures and compatibility with back-end-of-line (BEOL) processes.

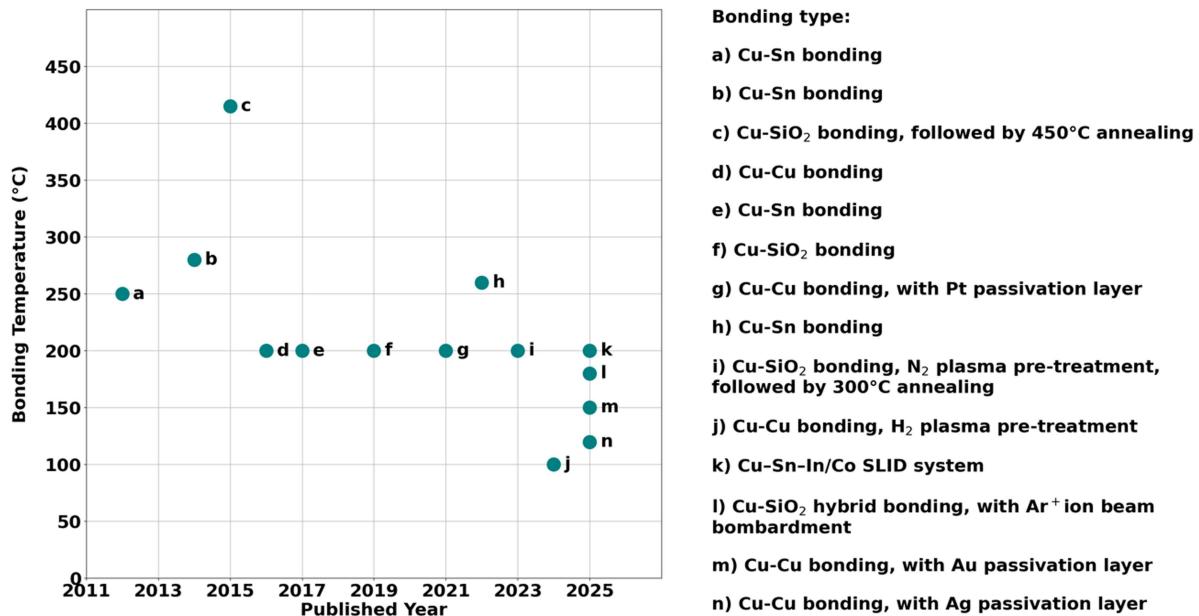

The most promising packaging solution for 3D ICs is the use of TSVs for bonding of die from different layers. Compared with monolithic 3D integration, the stacking sequence in TSVs is not strictly limited by thermal budgets because the chips are connected by through-silicon vias after fabricating devices on individual chips. In TSV formation processes, chemical mechanical planarization (CMP) is commonly applied to improve stress uniformity, eliminate Cu protrusion, and avoid package warpage [35,36]. Various materials can be used for bonding formation, including metal, oxide, and polymer. Metal bonding enables chips to be electrically connected, which is conventionally formed by thermal compression. Cu is the widely used metal due to its outstanding thermal and electrical properties. However, direct Cu-Cu bonding formation requires high temperature, which may not meet the thermal budget. Efforts have been made to lower the bonding temperature, such as applying hybrid bonding, surface-activation bonding, passivation layers, and other novel bonding methods. Figure 4 shows the trend of approaching lower processing temperatures in TSVs. Direct oxide bonding mainly serves as insulating layers, which can be formed at room temperature via van der Waals forces. Nevertheless, this kind of bonding typically requires further annealing to high temperatures to increase stability. Polymer bonding mainly serves as adhesion layers, which play an important role in providing mechanical support. Due to the larger size of vias, wafer thinning and keep-out zones are required in TSVs packaging. Wafer thinning not only assists with the

**Figure 3.** Evolution of the number of parameters used in state-of-the-art models (black) and memory capacity (red). The number of parameters utilised in transformer models increases by 410 $\times$  every 2 years while the memory capacity only grows at 2 $\times$  every 2 years. GPU memory is plotted by dividing memory size by six as approximate upper bound of the largest model which can be trained with corresponding memory (adapted with permission from [29]).

**Table 1.** Comparison of 2D, 2.5D and 3D packaging techniques.

| Packaging type          | Advantages                                                                         | Disadvantages                                                                                     |

|-------------------------|------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| 2D (planar packaging)   | Mature packaging, low cost, high yield, simple processing                          | Long interconnections, low interconnect density, high power consumption                           |

| 2.5D (interposer-based) | High bandwidth interconnections, easier thermal management compare to 3D solutions | Limited vertical integration, interposer increases the cost                                       |

| 3D TSV-based            | BEOL compatible, heterogeneous integration allowed                                 | Vias are large, keep-out zones are required, difficult uniform Cu via filling, Thermal challenges |

| 3D Monolithic           | Ultra-thin and dense vertical interconnections, heterogeneous integration allowed  | Difficult thermal budget management, high process complexity                                      |

| 3D Hybrid bonding       | Fine-pitch, high-density interconnections                                          | High alignment difficulty, CTE mismatch                                                           |

\*BEOL: Back end of line, CTE: Coefficient of thermal expansion.

miniaturisation of IC packaging but also enables the vias to connect both sides of the wafer. However, wafers tend to become fragile after the wafer thinning process. Therefore, chips are often temporarily bonded and de-bonded on a carrier wafer through heating or exposing polymer adhesive layers to ultraviolet lasers [37,38]. For instance, photosensitive polyimide [39], Brewer Science polymer [40] are reported in recent studies.

#### 4 Design methodologies for thermally efficient 3D ICs

3D ICs technology offers many advantages compared to 2D ICs designs. However, the vertical integration of multiple active layers results in increased power densities, consequently leading to higher on-chip

**Figure 4.** Approaches to lowering bonding temperatures in TSV packaging. This data is obtained from [41–54].

temperature [55,56]. High on-chip temperature can have adverse effects on the performance and reliability of the stacked system. Reliability issues such as electromigration (EM) and negative-bias-temperature instability (NBTI) become more pronounced with increasing temperature [57–59]. As discussed in section 3, formation of defect-free TSVs is critical to achieving better performance, and this can be achieved by reducing wafer thickness. However, reduction in wafer thickness can limit heat dissipation through the wafers due to phonon scattering at the interface layers [60]. Phonon scattering becomes dominant at higher temperatures, resulting in increased interconnect delay and leakage power, and can even lead to thermal runaway. The stacked system also consists of dielectric and adhesive bonding materials, which essentially limit the heat transfer paths due to their high thermal resistances [61]. In 3D ICs, the bottom side is generally equipped with electrical circuits, so only the top side may be available for heat dissipation for state-of-the-art cooling techniques. Therefore, implementing thermal-conscious design methodologies is crucial for efficient 3D ICs development. Here, we review recent studies on thermal designs for 3D ICs and discuss their solution schemes to overcome thermal challenges through efficient engineering.

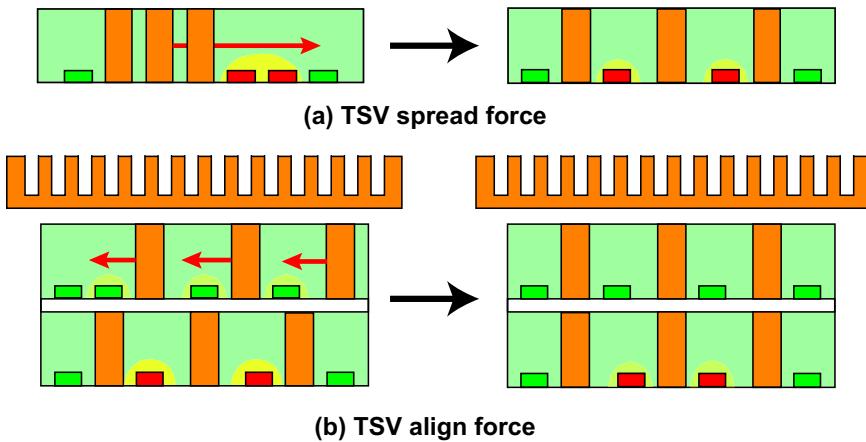

Conventionally, hotspot measurements of active chips can be conducted using experimental techniques such as Infra-red Thermography (IR), Thermoreflectance (TR) Microscopy, Scanning Thermal Microscopy (SThM) etc [62]. However, in 3D ICs, it is very challenging to conduct heat measurements for each individual die or layer [63]. Therefore, for accurate prediction of the temperature of each layer, the development of a corresponding heat transfer model is essential. There are various analytical and numerical approaches that are reported in the literature for modelling 3D ICs heat transport processes [64,65]. In 3D ICs, floorplanning, TSV placement, and routing are key important steps, and these steps should account for thermal-electrical co-design and co-optimisation [66]. Athikulwongse et al. developed a TSV spread and alignment algorithm to form a uniform thermal conductivity space and increase vertical overlap among TSVs across the dies in a 3D stack [67]. TSVs help dissipate power efficiently, so it is advantageous to position TSVs close to cells that dissipate high power density. Therefore, spreading TSVs according to cells' power-density dissipation may reduce local temperature and intra-die thermal variation in 3D ICs. Furthermore, this algorithm helps align TSVs from die to die to avoid heat constriction paths from TSV-adhesive or TSV-die interfaces (see Figure 5). Thermal-aware floorplanning is an inevitable step in the 3D IC design flow, as it involves determining the position of each cell on the wafer. Numerous design algorithms based on finite difference method (FDM), finite element method (FEM), B\*-tree, relaxed conflict net (RCN), and deep reinforcement learning have been proposed to enable thermal-aware floorplanning of 3D ICs [64,68,69]. In general, the weighted total interconnection wirelength ( $L_w$ ) is

**Figure 5.** (a) TSV Spread and (b) TSV Align algorithm based on power-density force optimisation (reproduced with permission from [67]).

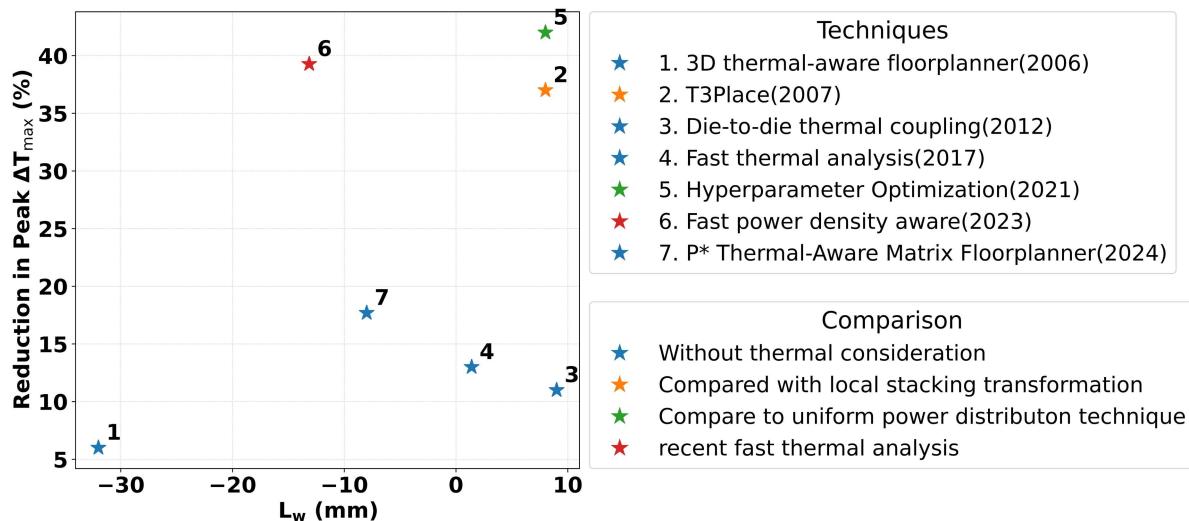

**Figure 6.** Reduction in peak temperature ( $\Delta T_{max}$ ) of top tier die and interconnection length ( $L_w$ ) reduction showed by different algorithms. This data is taken from [67–74].

widely accepted as the metric to evaluate the quality of different techniques. Therefore, in thermally aware placement, temperature is managed as a penalty to the wire-length ( $L_w$ ) objective function [64]. Figure 6 shows hotspot reduction ( $\Delta T_{max}$ ) and corresponding interconnection length ( $L_w$ ) reduction demonstrated by several floorplanning optimisation techniques from the recent reports in literature.

In 3D ICs, it is challenging to remove heat from intermediate layers with increasing numbers of stacked layers. A major concern is that the Si-layer with thickness  $<1\mu\text{m}$  exhibits a 2-fold lower thermal conductivity than its bulk form [75]. Therefore, 3D ICs cannot rely on spontaneous heat dissipation through Si. If the heat is not removed efficiently, thermomechanical stress arises around the TSVs due to the generated thermal gradients, which leads to serious reliability concerns [76]. Conventional cooling techniques such as air-cooling, liquid-cooling, backside heat exchangers, or thermoelectric coolers are not appropriate choices for 3D ICs because of their inability to reach intermediate layers. Therefore, it is crucial to develop efficient thermal management strategies and cooling techniques to unlock the full potential of stacked systems. The material choice of dielectrics and adhesives is the rate-determining step of heat transfer through layers. Körögölü et al. proposed replacing the thermally resistive interlayer dielectrics with high thermal conductivity electric

insulators such as AlN and hexagonal BN (hBN). AlN is an isotropic, high thermal conductivity material that efficiently removes heat from intermediate layers of a 3D stack. Whereas hBN is a strongly anisotropic, high thermal conductivity material that helps reduce hotspot peak temperatures [77].

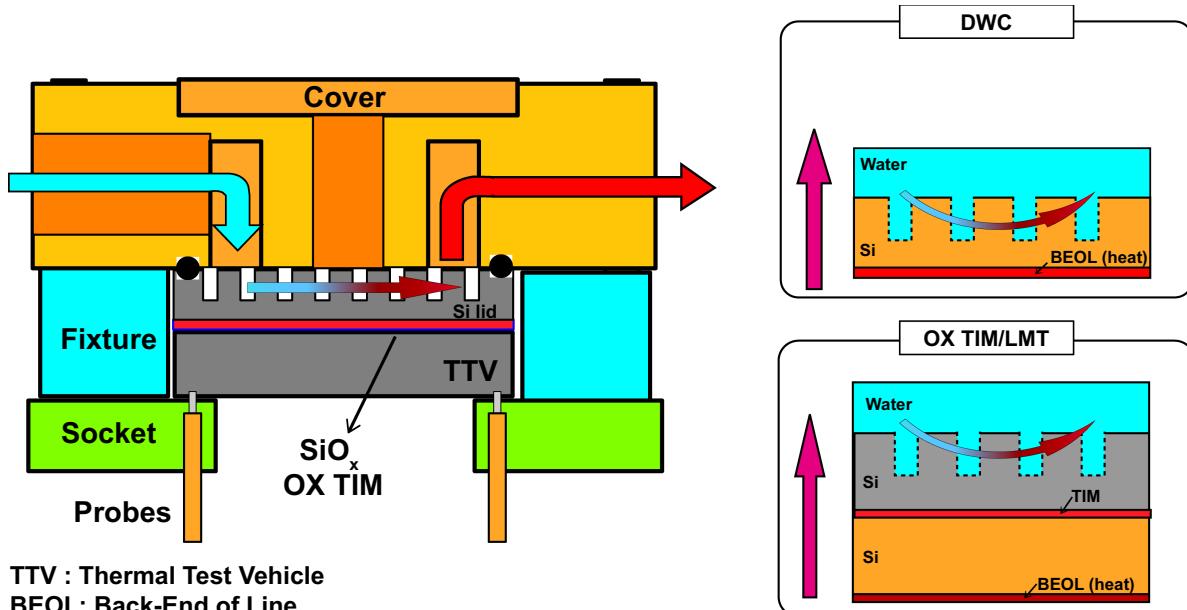

All 3D ICs design options face the challenge of ineffectiveness in removing heat from the intermediate heat-dissipating layers. Most techniques rely on an array of TSVs [61]. Wei et al. developed a power delivery networks (PDNs) based framework for delivering noise-free power which also contributes to the heat removal from intermediate layers [78]. This PDNs framework uses the inter-layer vias (ILVs) for connecting different components belonging to different layers of 3D ICs. Their simulation results show that PDNs can reduce the maximum steady-state temperature by 35 °C for a 2-layer monolithic 3D IC. In the last few years, a significant number of researches have demonstrated the high performance of micro-channel liquid cooling technique through a variety of architectures [79–81]. For example, Tiwei et al. proposed a novel impingement-based liquid cooling solution, fabricated using low-cost polymer, to directly cool the backside of high-performance chip stacks in 3D ICs [82]. Furthermore, Wu et al. from TSMC invented a direct silicon-water cooling solution for ultra-high-power cooling for 3D ICs as shown in Figure 7. This technique successfully demonstrated high cooling performance with total power  $>2600$  W on a single silicon-on-Chip (SoC), equivalent to the power density of  $4.8$  W/mm $^2$  [83]. Modelling of thermal optimisation of 3D ICs requires heavy computational power due to the requirement of solving large partial differential equation (PDEs) systems. Recently, a variety of PDE solution schemes have been developed to solve complex geometries of 3D ICs architectures with appropriate boundary conditions. Liu et al. proposed a neural network-based framework named DeepOHeat. This is a physics-aware deep learning model to predict temperature fields in 3D ICs [84]. Table 2 shows a few recently developed cooling approaches and their corresponding outcomes. With these strategies, it is important to experimentally validate each technique and find a cost-effective thermal management solution for 3D ICs. The decision of which thermal management technique to implement for a specific chip design is dependent on its application and cost.

**Figure 7.** Schematic of the customised pin socket. An o-ring is utilised to achieve water sealing. Two trenches are designed in the cover to create a uniform flat plate flow through the Si pillar array. Right top image shows direct water cooling (DWC) and bottom image shows the addition of  $\text{SiO}_x$  thermal interface model (OX TIM)/Liquid metal TIM (LTM) (reproduced with permission from [83]).

**Table 2.** Recent Development in Cooling Techniques for Thermal Management in 3D ICs.

| Paper | Approach                                                                                         | Outcome                                                                                                                                                                                                                                | Year |

|-------|--------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| [85]  | Liquid jet impingement/multi-jet backside cooling                                                | Achieves heat transfer coefficients up to $6.25 \times 10^4 \text{ Wm}^{-2} \text{ K}^{-1}$ with a pump power as low as 0.3 W                                                                                                          | 2018 |

| [86]  | Embedded microfluidic cooling (die-per-layer microchannels, inter-tier or through-chip channels) | supports heat fluxes above $10^4 \text{ W/cm}^2$ with $<60 \text{ K}$ rise; enables active two-phase flow cooling directly within the stack                                                                                            | 2024 |

| [87]  | Thermal scaffolding with conductive dielectric materials                                         | Reduces footprint penalty from 10% to 5.5% due to 3D thermal scaffolding and simultaneously meets worst-case IR drop constraint of $<20 \text{ mV}$ at 0.7 V supply and peak temperature constraint of $<125 \text{ }^{\circ}\text{C}$ | 2024 |

| [88]  | Temperature-Effect Inversion based thermal management (TEI-LP)                                   | Achieves 17.8% and 16.3% reductions in energy consumption at 50 MHz and 100 MHz respectively                                                                                                                                           | 2024 |

| [89]  | Nano-engineered thin-film thermoelectric cooling                                                 | Thin-film thermoelectric modules offer 100–300% better coefficient-of-performance than bulk devices depending on operational scenarios                                                                                                 | 2025 |

## 5 Electrical performance and interconnect considerations

As semiconductor technology advances towards complex 3D architectures and heterogeneous integration, managing electrical performance and interconnects becomes a critical challenge. The move to stack multiple dies introduces a new set of issues that can have an impact on the reliability and speed of the entire system. This section explores several key considerations in this domain: (i) The degradation of signal integrity and introduction of delays in vertical interconnects like TSVs; (ii) The difficulties in delivering stable power across these stacked layers; (iii) The parasitic effects of TSVs and interposer routing; (iv) Increased crosstalk and noise coupling between tightly packed components; and (v) The crucial need to co-optimise electrical and thermal performance for overall system stability.

3D integration is already delivering link- and system-level gains relevant to automated interconnect planning. A self-timed 3 nm die-to-die (D2D) PHY demonstrates 8 Gb/s per pin at 0.7 V with 77 fJ/bit energy and about 44 Tb/s/mm<sup>2</sup> bandwidth density, indicating single-cycle hop latency at fine pitches [90]. A complementary 9  $\mu\text{m}$ -pitch PAM-4 D2D test vehicle in 5/6 nm reports 16 Gb/s per pin, 10.24 Tb/s aggregate bandwidth, 0.296 pJ/bit, and 17.9 Tb/s/mm<sup>2</sup>, showing a tileable, cluster-based path to throughput scaling [91]. Foundry guidance is consistent: the 3D interconnect roadmap targets about a 2 $\times$  node-to-node gain in energy-efficient performance (EEP) by shrinking SoIC bonding pitch roughly 70% per node, and reports multiple-fold density increases with as much as 87% dynamic-power reduction versus microbump for near-memory stacks, which provides useful bounds for lane count, pitch, and thermal-cooling co-design in automation [92].

At the system level, many-core bandwidth-latency-thermal co-optimisation links practical pitch choices with achievable performance, showing that sub-2  $\mu\text{m}$  vertical interconnects are a feasible threshold for unlocking higher core-to-memory bandwidth under thermal limits [93]. A comparative PPA study across heterogeneous 3D options quantifies technology-choice deltas: hybrid bonding yields up to 81.4% timing improvement versus 2D and 25.8% EDP reduction on commercial CPU-class designs, while signal-integrity analysis map how MIV (sub-micron), face-to-face, and microbump pitches create trade off between crosstalk and signal-to-noise ratio (SNR) for constraint generation [94]. For memory-bound automation, HBM on interposers provides a 4096-bit interface at around 1 GHz achieving roughly 512 GB/s peak bandwidth (Fury X example), illustrating wide-and-slow links that reduce energy per bit within surface capacity constraints [95]. In heterogeneous multi-tier compute-in-memory (CIM), electrical-thermal co-design sweeps identify a TSV diameter sweet spot of 1-3  $\mu\text{m}$  that balances throughput and density with IR-drop and temperature, which is actionable for tier-to-tier channel sizing and thermal-aware routing [96].

In 3D ICs, signal quality through vertical interconnections like TSVs presents significant reliability and performance challenges. These vertical channels are subject to parasitic parameters-resistance, capacitance, and inductance that degrade signal waveforms and introduce noise [97]. Moreover, the compact stacking of dies intensifies signal latency, which can lead to synchronisation mismatches and impair system timing [98].

Parasitic phenomena intrinsic to TSV structures, especially resistance and capacitance, play a central role in signal loss and propagation delay [99]. As the number of stacked layers grows, the interconnect density rises, leading to shorter inter-layer paths that still exhibit greater signal distortion due to increased

coupling. This can result in timing violations and data integrity issues, especially in high-throughput designs [100].

To alleviate these concerns, multiple engineering approaches are employed. Fine-tuning the physical attributes of TSVs—such as minimising via diameter, selecting low-resistivity materials, and adopting more efficient via geometries help in mitigating signal degradation [100]. Complementary circuit-level techniques, including the deployment of buffers, amplifiers, and clock distribution frameworks, further enhance signal robustness and reduce timing skew [97]. A comparative summary of innovative vertical interconnect solutions—including carbon nanotube (CNT) TSVs, photonic interconnects, and adaptive buffer insertion—is presented in [Table 3](#).

Delivering stable and reliable power across vertically stacked dies remains a key bottleneck in 3D IC architectures. Due to the constrained footprint and elevated current demands, ensuring even voltage distribution becomes increasingly complex as the layer count rises [106]. A major concern in this context is the IR drop—voltage reduction along resistive paths—which can lead to insufficient power delivery in upper tiers and potentially jeopardise system operation [107].

As stacking becomes more aggressive, the interplay of TSV-related parasitic inductance and capacitance increasingly impacts the PDN, creating voltage ripple and transient instability [106]. If left unaddressed, such issues may escalate into performance losses or functional failures under dynamic workloads [107].

To enhance power integrity in 3D ICs, various strategies have emerged. Layer-specific power planes can help in maintaining localised voltage levels and improving power uniformity [106]. Employing low-resistivity materials in power and ground networks and optimising the TSV layout are also effective in minimising resistive losses [107]. Additionally, advanced PDN modelling and simulation techniques can be used proactively to forecast hotspots and guide the design of more resilient power delivery frameworks [99]. [Table 4](#) outlines key innovations in this space, including fine-grained voltage regulation, hybrid integration schemes, and thermal-aware co-design methodologies.

Parasitic effects inherent to TSVs, notably resistance (R), capacitance (C), and inductance (L), pose major design challenges in 3D integrated circuits [113]. These parasitics not only cause signal degradation and delay but

**Table 3.** Overview of Vertical Interconnect Technologies for Signal Integrity and Delay Improvement.

| Paper | Name                                       | Category                        | Year | Advantages                                                                                                                                                                |

|-------|--------------------------------------------|---------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [101] | TSV Interposer Integrated X-band Filter    | Electrical Optimisation Methods | 2019 | Low insertion loss (2.2 dB), wide bandwidth (2.33 GHz), small group delay variation (52 ps); uses high-resistivity silicon to reduce substrate loss and enhance Q factor. |

| [102] | CNT-based Tapered TSV Structures           | Material Innovation             | 2022 | Tapered single-/multi-wall CNTs reduce crosstalk-induced delay (by ~22.8%) and peak noise; lower power loss and improved transmission/reflection loss vs. Cu-based TSVs.  |

| [103] | Edge Coupler Integrated TSV Optical Module | System-Level Integration        | 2023 | Enhanced signal bandwidth and reduced delay through direct EIC–PIC interconnect using TSVs; low insertion loss (<0.35 dB @ 67 GHz), clean eye diagrams at 112 Gbps.       |

| [104] | Hollow Tungsten TSV (W-TSV)                | Structural Optimisation         | 2024 | Reduces thermal-induced stress by 60.3%, keeps surface stress below 31.02 MPa; no KOZ required, enabling denser integration and better signal reliability.                |

| [105] | GNR Interconnect with Buffer Insertion     | Routing and Layout Strategies   | 2025 | Simultaneous reduction in interconnect resistance (>30%) and delay (>40%) via optimal buffer placement; improves both signal and power integrity.                         |

**Table 4.** Summary of power delivery optimisation techniques.

| Paper | Name                                                                                  | Category                        | Year | Advantages                                                                                                                |

|-------|---------------------------------------------------------------------------------------|---------------------------------|------|---------------------------------------------------------------------------------------------------------------------------|

| [108] | Hybrid-Bonding 3D IC with Inter-Tier Metal Sharing and MIM Decap Sharing              | Material Innovation             | 2022 | Reduces dynamic IR-drop by up to 77 mV; achieves 17 mV less static IR-drop than micro-bumps; up to 76% performance boost. |

| [109] | Fully Integrated Voltage Regulator (FIVR)-based Power Delivery Methodology for 3D ICs | Electrical Optimisation Methods | 2022 | 5× reduction in power loss and 24× IR-drop reduction in 5-layer 3D stack.                                                 |

| [110] | Hybrid Bonded Backside PDN with nTSVs and CuPads                                      | Structural Optimisation         | 2023 | 69% average IR-drop reduction vs. frontside; nTSVs improve IR-drop over $\mu$ TSVs by 81% (avg) and 77% (peak).           |

| [111] | Iterative Layout-Aware Electrothermal Co-Optimisation (LoM Stack)                     | Routing and Layout Strategies   | 2025 | 6 °C lower temperature in LoM vs. MoL; 54% IR-drop reduction using tighter PDN pitch.                                     |

| [112] | 3D Heterogeneously Integrated Digital DC/DC Power Module for Vertical Power Delivery  | System-Level Integration        | 2025 | Power density of 1468 W/in <sup>3</sup> , >96% efficiency, <1% voltage ripple, and improved IR loss.                      |

also complicate timing closure and increase the likelihood of timing violations, especially as interconnect density increases with more stacked layers. High resistance and capacitance along TSVs lead to increased RC delay and signal attenuation. Their large size and proximity further cause coupling capacitance between adjacent TSVs, intensifying crosstalk and noise interference. Imperfect TSV processing may introduce defects-for example, resistive opens or bridges-leading to further deterioration of signal quality due to increases in RC delay. In addition, interposer routing introduces additional parasitic load and longer signal paths, which can degrade both signal and power integrity, especially important as system complexity grows [114].

Mitigation strategies include optimising TSV physical parameters (smaller diameter, strategic placement, and selection of low-loss liner materials), use of shielding or guard TSVs, and evolving toward coaxial or advanced CNT-filled TSVs to reduce parasitics and improve high-frequency performance [115,116]. Thorough post-bond testing and redundancy in TSV design also help maintain reliability in large-scale 3D-IC implementations [117,118].

Crosstalk-the undesirable coupling of signals between adjacent TSVs-remains a significant challenge in high-density 3D stacking [119]. Closely packed TSVs, especially those transmitting high-frequency signals, generate electrostatic and electromagnetic interference due to the strong coupling capacitance between them. This can result in signal integrity issues such as increased jitter, false toggling, or data corruption, ultimately limiting achievable bandwidth and performance.

Several factors influence TSV crosstalk, including TSV pitch, diameter, dielectric environment, and routing topology. Embedding ground TSVs between signal TSVs and optimising their spatial arrangement can notably reduce noise coupling. In addition, advanced TSV structures such as CNT-filled, tapered, or coaxial TSVs have demonstrated reductions in crosstalk-induced delay and power dissipation [115,120]. On the algorithmic side, crosstalk-aware channel encoding and adaptive crosstalk avoidance coding further mitigate the risk for highly parallel channels [114]. **Table 5** outlines some approaches to mitigate crosstalk and noise issues. These combined materials, physical configurations, and signal processing approaches help preserve signal integrity in future large-scale 3D ICs.

The electrical and thermal behaviours of 3D ICs are deeply intertwined, necessitating a holistic co-design approach. High power densities in stacked dies intensify self-heating and thermal gradients, which affect TSV reliability, induce thermomechanical stress, and may ultimately degrade electrical performance due to increased resistance, leakage, and electromigration. Simultaneously, TSVs can be leveraged as both electrical conductors and thermal conduits; their placement and density thus influence both IR-drop and heat distribution [113].

Co-optimisation techniques-such as thermal-aware floor planning, placement-driven TSV and power grid design, and coupled electro-thermal simulation-are critical for next-generation 3D systems [124]. Recent works have demonstrated that evolutionary floor planning algorithms and iterative layout-aware co-optimisation significantly improve both temperature profiles and IR-drop targets in complex stacks as discussed in the previous section. Incorporating high-thermal-conductivity materials in dielectric and adhesive layers, as well as optimising microchannel cooling proximity to hotspots, produces further benefits at the system level. Ultimately, such integrated co-design methodologies are essential to achieve robust, power-efficient, and high-performance 3D ICs that can strengthen future intelligent computing platforms.

**Table 5.** Summary of crosstalk and noise mitigation techniques.

| Paper | Name                             | Year | Advantages                                                                                                                                                                                      |

|-------|----------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [121] | Grounded Shields/Guard Rings     | 2014 | Reduces capacitive coupling by isolating sensitive nets from aggressors and creating a more effective discharging path.                                                                         |

| [119] | Optimised Routing (Net Spacing)  | 2018 | Increases the physical distance between TSVs and other signal paths, which diminishes electromagnetic coupling and its resulting crosstalk.                                                     |

| [121] | Differential Signalling          | 2014 | Transmits a signal using a pair of conductors. This method provides superior noise immunity by effectively rejecting common-mode noise that is coupled to both lines.                           |

| [122] | Crosstalk Avoidance Codes (CACs) | 2017 | Involves remapping data bits before transmission in a way that minimises the crosstalk generated. This can reduce crosstalk on TSVs and metal wires by approximately 30% and 50%, respectively. |

| [123] | Tapered TSV Structures           | 2023 | Utilising TSVs with a tapered shape can effectively lower crosstalk-induced delay, thermomechanical stress, and the power-delay product (PDP).                                                  |

| [119] | Adding Reference (Ground) Vias   | 2018 | Incorporating additional ground vias helps to establish well-defined return paths for the current, which has a significant impact on mitigating crosstalk.                                      |

As high-performance computing (HPC) and AI systems continue to scale, the interconnects between processors, accelerators, and memory have become a primary performance bottleneck. High-speed Serializer/Deserializer (SerDes) interfaces, which form the backbone of data centre communication, are now pushing data rates to 56 Gbps, 112 Gbps, and beyond [125,126]. In traditional systems, these electrical signals must travel long distances across printed circuit boards (PCBs) to reach front-panel pluggable optical modules, leading to significant signal degradation, high power consumption, and latency, which collectively limit system bandwidth and scalability [127].

Advanced 3D IC packaging provides a transformative solution to this challenge through the heterogeneous integration of co-packaged optics (CPO). CPO involves placing optical I/O engines on the same package substrate as the primary silicon die, like a switch ASIC or an accelerator. This architecture dramatically shortens the length of the high-speed electrical traces from tens of centimeters to just a few millimetres [127]. The result is a substantial reduction in the power required to drive the SerDes links, improved signal integrity due to lower channel loss, and a massive increase in bandwidth density at the chip edge. By converting high-speed electrical signals to optical signals closer to the source, 3D packaging with CPO effectively bypasses the conventional interconnect bottlenecks that hinder the performance of large-scale computing systems.

The implementation of CPO relies heavily on the capabilities of advanced packaging technologies, including 2.5D and 3D integration, which enable the dense and reliable interconnection of both copper and optical components [128]. For instance, the use of glass core substrates (GCS) is emerging as a key enabler, offering superior dimensional stability and electrical properties needed to support the large package sizes and fine-pitch interconnects required for AI and HPC applications utilising CPO [129]. These advanced packaging techniques are crucial not only for the ASIC-to-optics interface but also for optimising the high-density copper traces and TSVs that are integral to the package design [130]. This synergy between 3D packaging and co-packaged optics represents a critical path for breaking through the memory wall and interconnect-scaling limitations in the next generation of high-performance computers [131].

## 6 Summary and outlook

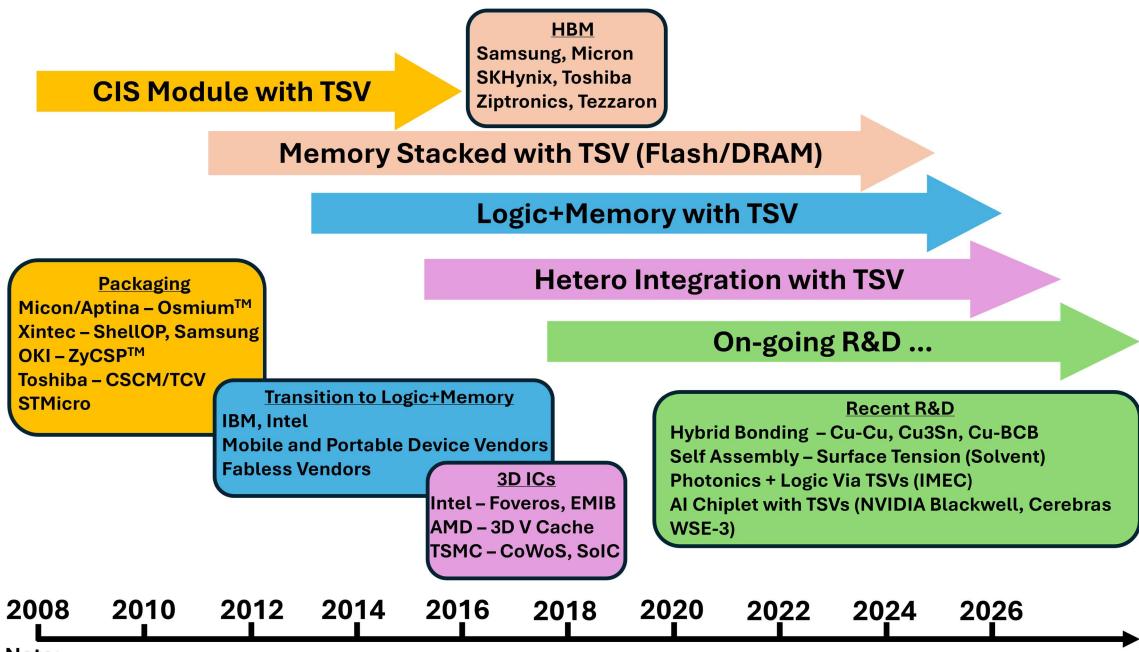

3D integrated circuit (3D ICs) technology has evolved significantly since its first commercial deployment in image sensor modules in the late 2000s (Figure 8). The concept was initially driven by the formation of through-silicon vias (TSVs) to enable vertically stacked systems. Since then, 3D ICs have gained momentum in both research and product development. Early industrial adoption focused on applications such as image sensors and DRAM stacking, with high-bandwidth memory (HBM) emerging as a landmark achievement in stacking technology. It has now been nearly a decade since Micron and Samsung began mass-producing HBM for data-intensive AI workloads. Emerging paradigms such as BEOL-compatible oxide-semiconductors, processing-in-memory (PIM) or computing-in-memory (CIM), and neuromorphic computing have further accelerated interest in 3D IC-based computing platforms.

Packaging remains one of the most critical aspects of stacked device technology, requiring highly advanced bonding processes. Although substantial progress has been made in both temporary and permanent bonding techniques, several key challenges still remain. The fabrication of high aspect-ratio (AR) TSVs is particularly demanding as the number of stacked dies increases. Uniform deposition in such TSVs is difficult to achieve due to defect formation during processing, and reliable defect characterisation remains a major hurdle. Companies such as Carl Zeiss and Bruker are developing dedicated metrology tools to address TSV defect detection, while machine learning approaches-including neural network-based frameworks-are being explored to enhance defect analysis.

Other pressing research areas include the handling of carrier wafers, optimisation of temporary/permanent bonding materials, integration of thermal interface materials (TIMs), TSVs alignment, and the co-design of these factors with thermal management strategies. Design consideration of the thermal budget for the bottom die in a stack is mostly lacking in the literature. Incorporating thermal management strategies early in the 3D ICs design flow is essential. Most reported heat transfer models adopt simplified architectures that overlook real-world physical complexities. Developing more sophisticated and realistic thermal transport models is critical for accurately predicting heat dissipation across all layers, with

**Figure 8.** Major timeline of 3D system technology development and future outlook.

particular emphasis on the thermal behaviour of intermediate layers, which is vital for ensuring product reliability.

Although some studies have addressed intermediate-layer thermal management through optimised power delivery network (PDN) architectures, the effective mitigation of localised hotspots in these regions remains largely unexplored. Cooling technologies tailored for 3D ICs are still in their early stages. While microfluidic cooling shows strong potential for stacked systems, it must be co-optimised with other reliability parameters, such as dielectric loss minimisation, to ensure overall system performance. Currently, the major research thrust of 3D ICs technology is focused on optimising electrical and thermal performance and leveraging its advantages through heterogeneous integration (HI). However, for a smooth transition from academia to industry, yield and cost at manufacturing scale must be considered. Multiple models now guide cost-aware flow selection for stacked systems. Taouil's PhD thesis develops yield/cost formulations that capture stack-level defect compounding and the role of pre-/mid-/post-bond test and repair in overall economics [132]. At the system level, Dong and Xie et al. analyse how partitioning choices and integration flows drive total cost, while Chen et al. emphasise the testing component and design-for-test overheads as key levers in cost-effective 3D integration [133,134]. More recently, Jeloka et al. frame these trade-offs in a contemporary system-technology co-optimisation context, highlighting how advances in bonding pitch and power-delivery constraints shift cost/performance break-even points among flows [135]. In parallel, standardisation is progressing: IEEE Std 1838 defines a test-access architecture for three-dimensional stacked ICs, linking cost/yield insights to actionable design for testability (DfT) practice and enabling interoperable test strategies across dies and stacks [136]. Broader adoption of such standards in the design, fabrication, and testing workflows will be an important step toward the large-scale commercialisation of 3D ICs technology.

In conclusion, while 3D ICs present significant fabrication, thermal, and reliability challenges, rapid advancements in simulation, manufacturing, and characterisation techniques are steadily making them a more practical solution for next-generation computing demands. The formation of global 3D ICs research consortia reflects a coordinated push across academia and industry to address these challenges. The development of 3D ICs technology spans multiple engineering disciplines, requiring interdisciplinary collaboration to bring the technology to mainstream consumer applications. This review provides

researchers and practitioners with a consolidated view of the current state of 3D ICs, along with key challenges and future directions for this transformative technology.

## Disclosure statement

The authors declare no competing financial interest.

## ORCID

Ram Eknath Munde  0009-0001-5597-1213

Raisul Islam  0000-0002-1222-6117

## References

- [1] Moore GE. Cramming more components onto integrated circuits. **1965**.

- [2] Dennard RH, Gaenslen FH, Yu HN, et al. Design of ion-implanted mosfet's with very small physical dimensions. *IEEE J Solid State Circ*. **2003**;9(5):256–268. doi: [10.1109/JSSC.1974.1050511](https://doi.org/10.1109/JSSC.1974.1050511)

- [3] Dennard RH, Cai J, Kumar A. A perspective on today's scaling challenges and possible future directions. In: *Handbook of Thin Film Deposition*. Elsevier; **2018**. pp. 3–18.

- [4] Johnsson L, Netzer G. The impact of moore's law and loss of dennard scaling: are dsp socs an energy efficient alternative to x86 socs? *J Phys Conf Ser*. **2016**;762:012022. IOP Publishing. doi: [10.1088/1742-6596/762/1/012022](https://doi.org/10.1088/1742-6596/762/1/012022)

- [5] Kumar R, Zyuban V, Tullsen DM. Interconnections in multi-core architectures: understanding mechanisms, overheads and scaling. In: *32nd International Symposium on Computer Architecture (ISCA'05)*. IEEE; **2005**. pp. 408–419. doi: [10.1109/ISCA.2005.34](https://doi.org/10.1109/ISCA.2005.34)

- [6] Bohr MT, Young IA. Cmos scaling trends and beyond. *IEEE Micro*. **2017**;37(6):20–29. doi: [10.1109/MM.2017.4241347](https://doi.org/10.1109/MM.2017.4241347)

- [7] Sharma E, Rathi R, Misharwal J, et al. Evolution in lithography techniques: microlithography to nanolithography. *Nanomaterials*. **2022**;12(16):2754. doi: [10.3390/nano12162754](https://doi.org/10.3390/nano12162754)

- [8] Levinson HJ. High-na euv lithography: current status and outlook for the future. *JaJAP*. **2022**;61(SD):0803. doi: [10.35848/1347-4065/ac49fa](https://doi.org/10.35848/1347-4065/ac49fa)

- [9] Batra G, Jacobson Z, Madhav S, et al. Artificial intelligence hardware: new opportunities for semiconductor companies. *McKinsey and Company*; **2019**. Vol.2.

- [10] Welser J, Pitera JW, Goldberg C. Future computing hardware for AI. *2018 IEEE International Electron Devices Meeting (IEDM)*. **2018**. pp. 21–23. doi: [10.1109/IEDM.2018.8614482](https://doi.org/10.1109/IEDM.2018.8614482)

- [11] Kurshan E, Franzon P. 3D stacking for ai systems: emulating heterogeneous 3D architectures for AI. *IEEE Trans Compon Packag Manuf Technol*. **2025**;15:1161–1169. doi: [10.1109/TCPT.2025.3567201](https://doi.org/10.1109/TCPT.2025.3567201)

- [12] Kurshan E, Franzon PD. Towards 3D AI hardware: fine-grain hardware characterization of 3D stacks for heterogeneous system integration & AI systems. *2024 International 3D Systems Integration Conference (3DIC)*. IEEE; **2024**. p. 1–6.

- [13] Burns J, McIlrath L, Keast C, et al. Three-dimensional integrated circuits for low-power, high-bandwidth systems on a chip. In: *2001 IEEE International Solid-State Circuits Conference. Digest of Technical Papers. ISSCC (Cat. No. 01CH37177)*. IEEE; **2001**. pp. 268–269. doi: [10.1109/ISSCC.2001.912632](https://doi.org/10.1109/ISSCC.2001.912632)

- [14] Liu CC, Ganusov I, Burtscher M, et al. Bridging the processor-memory performance gap with 3d ic technology. *IEEE Des Test Comput*. **2005**;22(6):556–564. doi: [10.1109/MDT.2005.134](https://doi.org/10.1109/MDT.2005.134)

- [15] Banerjee K, Souri SJ, Kapur P, et al. 3-d ics: a novel chip design for improving deep-submicrometer interconnect performance and systems-on-chip integration. *Proc IEEE*. **2002**;89(5):602–633. doi: [10.1109/5.929647](https://doi.org/10.1109/5.929647)

- [16] Pavlidis VF, Friedman EG. Interconnect-based design methodologies for three-dimensional integrated circuits. *Proc IEEE*. **2009**;97(1):123–140.

- [17] Black B, Annavaram M, Brekelbaum N, et al. Die stacking (3d) microarchitecture. In: *2006 39th Annual IEEE/ACM International Symposium on Microarchitecture (MICRO'06)*. IEEE; **2006**. pp. 469–479. doi: [10.1109/MICRO.2006.18](https://doi.org/10.1109/MICRO.2006.18)

- [18] Kim K, Park M-j. Present and future, challenges of high bandwidth memory (hbm). In: *2024 IEEE International Memory Workshop (IMW)*. **2024**. pp. 1–4. doi: [10.1109/IMW59701.2024.10536972](https://doi.org/10.1109/IMW59701.2024.10536972)

- [19] <https://www.intel.com/content/www/us/en/foundry/packaging.html>

- [20] Saraswat KC. 3-d ics: motivation, performance analysis, technology and applications. In: *2010 17th IEEE International Symposium on the Physical and Failure Analysis of Integrated Circuits*. IEEE; **2010**. p. 1–6. doi: [10.1109/IPFA.2010.5532301](https://doi.org/10.1109/IPFA.2010.5532301)

- [21] <https://www.amd.com/en/products/processors/technologies/3d-v-cache.html>

- [22] Hu C, Chen M, Chiou W, et al. 3d multi-chip integration with system on integrated chips (soic™). In: *2019 Symposium on VLSI Technology*. Kyoto, Japan. **2019**. pp. T20–T21. doi: [10.23919/VLSIT.2019.8776486](https://doi.org/10.23919/VLSIT.2019.8776486)

[23] Zhu S, Yu T, Xu T, et al. Intelligent computing: the latest advances, challenges, and future. *Intell Comput.* **2023**;2:0006. doi: [10.34133/icomputing.0006](https://doi.org/10.34133/icomputing.0006)

[24] Tan CS, Chen KN, Koester SJ. 3D Integration for VLSI Systems. CRC Press; **2016**.

[25] Kurshan E, Franzon P. 3-d stacking for ai systems: emulating heterogeneous 3-d architectures for AI. *IEEE Trans Compon Packag Manuf Technol.* **2025**;15(6):1161–1169. doi: [10.1109/TCPMT.2025.3567201](https://doi.org/10.1109/TCPMT.2025.3567201)

[26] Kurshan E, Franzon PD. Towards 3d ai hardware: fine-grain hardware characterization of 3d stacks for heterogeneous system integration & ai systems. In: 2024 International 3D Systems Integration Conference (3DIC). **2024**. pp. 1–6.

[27] Kaplan J, McCandlish S, Henighan T, et al. Scaling laws for neural language models. **2020**. arXiv preprint arXiv:2001.08361.

[28] Lau JH. Recent advances and trends in heterogeneous integrations. *J Microelectron Electron Packag.* **2019**;16(2):45–77. doi: [10.4071/imaps.780287](https://doi.org/10.4071/imaps.780287)

[29] Gholami A, Yao Z, Kim S, et al. Ai and memory wall. *IEEE Micro.* **2024**;44(3):33–39. doi: [10.1109/MM.2024.3373763](https://doi.org/10.1109/MM.2024.3373763)

[30] Bishop MD, Wong HSP, Mitra S, et al. Monolithic 3-d integration. *IEEE Micro.* **2019**;39(6):16–27. doi: [10.1109/MM.2019.2942982](https://doi.org/10.1109/MM.2019.2942982)

[31] Kim KS, Seo S, Kwon J, et al. Growth-based monolithic 3d integration of single-crystal 2d semiconductors. *Nature.* **2024**;636(8043):615–621. doi: [10.1038/s41586-024-08236-9](https://doi.org/10.1038/s41586-024-08236-9)

[32] Pendurthi R, Sakib NU, Sadaf MUK, et al. Monolithic three-dimensional integration of complementary two-dimensional field-effect transistors. *Nat Na.* **2024**;19(7):970–977. doi: [10.1038/s41565-024-01705-2](https://doi.org/10.1038/s41565-024-01705-2)

[33] Zhou X, Wang K, Liu Y, et al. Low-temperature fabricated amorphous oxide semiconductor heterojunction diode for monolithic 3d power integration applications. In: 2021 33rd International Symposium on Power Semiconductor Devices and ICs (ISPSD). IEEE; **2021**. pp. 283–286. doi: [10.23919/ISPSD50666.2021.9452201](https://doi.org/10.23919/ISPSD50666.2021.9452201)

[34] Zhang Y, Li J, Li J, et al. 3-masks-processed sub-100 nm amorphous ingazno thin-film transistors for monolithic 3d capacitor-less dynamic random access memories. *Adv Electron Mater.* **2023**;9(8):2300150. doi: [10.1002/aelm.202300150](https://doi.org/10.1002/aelm.202300150)

[35] Wang S, Zhang H, Tian Z, et al. Optimization of cu protrusion of wafer-to-wafer hybrid bonding for hbm packages application. *Mater Sci Semicond Process.* **2022**;152:107063. doi: [10.1016/j.mssp.2022.107063](https://doi.org/10.1016/j.mssp.2022.107063)

[36] Liu T, Wang S, Dong F, et al. Study of the protrusion of through-silicon vias in dual annealing-cmp processes for 3d integration. *Microsyst and Nanoeng.* **2025**;11(1):25. doi: [10.1038/s41378-024-00797-z](https://doi.org/10.1038/s41378-024-00797-z)

[37] Wang F, Liu Q, Li J, et al. Oriented design of wafer-level stacking structures to enhance reliability of laser debonding of thin devices. *Opt Laser Technol.* **2024**;169:110169. doi: [10.1016/j.optlastec.2023.110169](https://doi.org/10.1016/j.optlastec.2023.110169)

[38] Xia Y, Ling B, Wang X, et al. Temporary protective packaging for vertical integration of optical-window-free tsv-based micromirror array. *IEEE Trans Compon Packag Manuf Technol.* **2024**;14(3):359–367. doi: [10.1109/TCPMT.2024.3362882](https://doi.org/10.1109/TCPMT.2024.3362882)

[39] Tominaga A, Shen J, Liu C, et al. Temporary adhesive effect on multichip thinning for rapid prototyping of 3d-ic from 2d-ic fabricated in foundry shuttle services. In: 2024 International 3D Systems Integration Conference (3DIC). IEEE; **2024**. pp. 1–3. doi: [10.1109/3DIC63395.2024.10830079](https://doi.org/10.1109/3DIC63395.2024.10830079)

[40] Montméat P, Bally L, Dechamp J, et al. Temporary polymer bonding for the manufacturing of thin wafers: an innovative low temperature process. *Mater Sci Semicond Process.* **2021**;123:105550. doi: [10.1016/j.mssp.2020.105550](https://doi.org/10.1016/j.mssp.2020.105550)

[41] Ko CT, Hsiao ZC, Chang YJ, et al. A wafer-level three-dimensional integration scheme with cu tsvs based on microbump/adhesive hybrid bonding for three-dimensional memory application. *IEEE Trans Device Mater Reliab.* **2012**;12(2):209–216. doi: [10.1109/TDMR.2012.2195005](https://doi.org/10.1109/TDMR.2012.2195005)

[42] Lv Y, Chen M, Cai M, et al. A reliable cu-sn stack bonding technology for 3d-tsv packaging. *Semicond Sci Technol.* **2014**;29(2):025003. doi: [10.1088/0268-1242/29/2/025003](https://doi.org/10.1088/0268-1242/29/2/025003)

[43] Kim SE, Kim S. Wafer level cu-cu direct bonding for 3d integration. *Microelectron Eng.* **2015**;137:158–163. doi: [10.1016/j.mee.2014.12.012](https://doi.org/10.1016/j.mee.2014.12.012)

[44] Xie L, Wickramanayaka S, Chong SC, et al. 6um pitch high density cu-cu bonding for 3d ic stacking. In: 2016 IEEE 66th Electronic Components and Technology Conference (ECTC). IEEE; **2016**. pp. 2126–2133. doi: [10.1109/ECTC.2016.141](https://doi.org/10.1109/ECTC.2016.141)

[45] Wang J, Wang Q, Wu Z, et al. Solid-state-diffusion bonding for wafer-level fine-pitch cu/sn/cu interconnect in 3-d integration. *IEEE Trans Compon Packag Manuf Technol.* **2016**;7(1):19–26. doi: [10.1109/TCPMT.2016.2626794](https://doi.org/10.1109/TCPMT.2016.2626794)

[46] Gao G, Mirkarimi L, Workman T, et al. Low temperature cu interconnect with chip to wafer hybrid bonding. In: 2019 IEEE 69th Electronic Components and Technology Conference (ECTC). IEEE; **2019**. pp. 628–635. doi: [10.1109/ECTC.2019.00100](https://doi.org/10.1109/ECTC.2019.00100)

[47] Liu D, Kuo TY, Liu YW, et al. Investigation of low-temperature cu-cu direct bonding with pt passivation layer in 3-d integration. *IEEE Trans Compon Packag Manuf Technol.* **2021**;11(4):573–578. doi: [10.1109/TCPMT.2021.3069085](https://doi.org/10.1109/TCPMT.2021.3069085)

[48] Shi Y, Wang Z, Kang J, et al. Bonding of 5  $\mu$ m cu-sn micro bumps using thermal reflow and solid-state pre-bonding. *IEEE Trans Compon Packag Manuf Technol.* **2022**;12(10):1609–1617. doi: [10.1109/TCPMT.2022.3213540](https://doi.org/10.1109/TCPMT.2022.3213540)

[49] Yao M, Hao X, Luo G, et al. A highly compatible and step-by-step temporary bonding and debonding strategy for ultra-thin wafer level package. In: 2023 IEEE International Conference on Manipulation, Manufacturing and Measurement on the Nanoscale (3M-NANO). IEEE; **2023**. pp. 114–118. doi: [10.1109/3M-NANO58613.2023.10305341](https://doi.org/10.1109/3M-NANO58613.2023.10305341)

[50] Chiu CH, Chen WT, Song JM. Surface modification for ultrasonic cu-to-cu direct bonding. In: 2024 International 3D Systems Integration Conference (3DIC). IEEE; **2024**. pp. 1–4. doi: [10.1109/3DIC63395.2024.10830091](https://doi.org/10.1109/3DIC63395.2024.10830091)

[51] Emadi F, Liu S, Vuorinen V, et al. Low-temperature slid-tsv interconnects for 3d (mems) packaging. *IEEE Trans Compon Packag Manuf Technol.* **2025**;15:377–386. doi: [10.1109/TCPMT.2025.3528519](https://doi.org/10.1109/TCPMT.2025.3528519)

[52] Abadie K, Renaud P, Fournel F, et al. Surface activated cu/sio2 hybrid bonding for room temperature 3d integration. *JaJAP.* **2025**;64(3):03SP07. doi: [10.35848/1347-4065/adb639](https://doi.org/10.35848/1347-4065/adb639)

[53] Lee S, Song J, Park S, et al. Effects of au passivation thickness on improving low-temperature cu-to-cu bonding interface. *IEEE Trans Compon Packag Manuf Technol.* **2025**;15:1351–1358. doi: [10.1109/TCPMT.2025.3526663](https://doi.org/10.1109/TCPMT.2025.3526663)

[54] Hsu MP, Chen CH, Hong ZJ, et al. Enhancement of low-temperature cu-cu bonding by metal alloy passivation in ambient atmosphere. *IEDL.* **2024**;45(8):1500–1503. doi: [10.1109/LED.2024.3416180](https://doi.org/10.1109/LED.2024.3416180)

[55] Tavakkoli F, Ebrahimi S, Wang S, et al. Analysis of critical thermal issues in 3d integrated circuits. *IJHMT.* **2016**;97:337–352. doi: [10.1016/j.ijheatmasstransfer.2016.02.010](https://doi.org/10.1016/j.ijheatmasstransfer.2016.02.010)

[56] Sekar D, King C, Dang B, et al. A 3d-ic technology with integrated microchannel cooling. In: *2008 International Interconnect Technology Conference*, pages. IEEE; **2008**. pp. 13–15.

[57] Tu KN, Liu Y. *Elements of Electromigration: Electromigration in 3D IC technology*. CRC Press; **2024**

[58] Lu T, Yang Z, Srivastava A. Electromigration-aware placement for 3d-ics. In: *2016 17th International Symposium on Quality Electronic Design (ISQED)*. IEEE; **2016**. pp. 35–40. doi: [10.1109/ISQED.2016.7479173](https://doi.org/10.1109/ISQED.2016.7479173)

[59] Liu Y, Liang L, Irving S, et al. 3d modeling of electromigration combined with thermal–mechanical effect for ic device and package. *Microelectron Reliab.* **2008**;48(6):811–824. doi: [10.1016/j.microrel.2008.03.021](https://doi.org/10.1016/j.microrel.2008.03.021)

[60] Foss CJ, Aksamija Z. Quantifying thermal boundary conductance of 2d–3d interfaces. *TDM.* **2019**;6(2):025019. doi: [10.1088/2053-1583/ab04bf](https://doi.org/10.1088/2053-1583/ab04bf)

[61] Guo F, Suo ZJ, Xi X, et al. Recent developments in thermal management of 3d ics: A review. *IEEE Access.* **2025**;13:94286–94301. doi: [10.1109/ACCESS.2025.3569879](https://doi.org/10.1109/ACCESS.2025.3569879)

[62] Cahill DG, Braun PV, Chen G, et al. Nanoscale thermal transport. ii. 2003–2012. *Appl Phys Rev.* **2014**;1(1):011305.

[63] Santos C, Vivet P, Colonna JP, et al. Thermal performance of 3d ics: analysis and alternatives. In: *2014 International 3D Systems Integration Conference (3DIC)*. IEEE; **2014**. pp. 1–7. doi: [10.1109/3DIC.2014.7152163](https://doi.org/10.1109/3DIC.2014.7152163)

[64] Salvi SS, Jain A. A review of recent research on heat transfer in three-dimensional integrated circuits (3-d ics). *IEEE Trans Compon Packag Manuf Technol.* **2021**;11(5):802–821. doi: [10.1109/TCPMT.2021.3064030](https://doi.org/10.1109/TCPMT.2021.3064030)

[65] Jain A, Jones RE, Chatterjee R, et al. Analytical and numerical modeling of the thermal performance of three-dimensional integrated circuits. *IEEE Trans Compon Packag Technol.* **2009**;33(1):56–63.

[66] Cong J, Luo G. Advances and challenges in 3d physical design. *IPSJ Transactions on System and LSI Design Methodology.* **2010**;3:2–18. doi: [10.2197/ipsjtsdm.3.2](https://doi.org/10.2197/ipsjtsdm.3.2)

[67] Athikulwongse K, Pathak M, Lim SK. Exploiting die-to-die thermal coupling in 3d ic placement In: *Proceedings of the 49th Annual Design Automation Conference*. **2012**. pp. 741–746. doi: [10.1145/2228360.2228495](https://doi.org/10.1145/2228360.2228495)

[68] Chang YC, Chang YW, Wu GM, et al. B\*-trees: a new representation for non-slicing floorplans. In: *Proceedings of the 37th annual design automation conference*, pages. **2000**. pp. 458–463. doi: [10.1145/337292.337541](https://doi.org/10.1145/337292.337541)

[69] Hung WL, Link GM, Xie Y, et al. Interconnect and thermal-aware floorplanning for 3d microprocessors. *7th International Symposium on Quality Electronic Design (ISQED'06)*. IEEE; **2006**. p. 6

[70] Al Saleh D, Safari Y, Amik FR, et al. P\* admissible thermalaware matrix floorplanner for 3d ics. In: *2023 IEEE 36th International Systemon- Chip Conference (SOCC)*. **2023**. pp. 1–6. doi: [10.1109/SOCC58585.2023.10256905](https://doi.org/10.1109/SOCC58585.2023.10256905)

[71] Meitei NY, Baishnab KL, Trivedi G. Fast power density aware three-dimensional integrated circuit floorplanning for hard macroblocks using best operator combination genetic algorithm. *Int J Circuit Theory Appl.* **2023**;51(10):4879–4896. doi: [10.1002/cta.3672](https://doi.org/10.1002/cta.3672)

[72] Cong J, Luo G, Wei J, et al. Thermal-aware 3d ic placement via transformation. In: *2007 Asia and South Pacific Design Automation Conference*. IEEE; **2007**. pp. 780–785. doi: [10.1109/ASPDAC.2007.358084](https://doi.org/10.1109/ASPDAC.2007.358084)

[73] Xu Q, Chen S. Fast thermal analysis for fixed-outline 3d floorplanning. *Integration.* **2017**;59:157–167. doi: [10.1016/j.vlsi.2017.06.013](https://doi.org/10.1016/j.vlsi.2017.06.013)

[74] Lin JM, Chang WY, Hsieh HY, et al. Thermal-aware floorplanning and tsv-planning for mixed-type modules in a fixed-outline 3-d ic. *IEEE Trans Very Large Scale Integr VLSI Syst.* **2021**;29(9):1652–1664. doi: [10.1109/TVLSI.2021.3100343](https://doi.org/10.1109/TVLSI.2021.3100343)

[75] Ju YS, Goodson KE. Phonon scattering in silicon films with thickness of order 100 nm. *Appl Phys Lett.* **1999**;74(20):3005–3007. doi: [10.1063/1.123994](https://doi.org/10.1063/1.123994)

[76] Wang J, Duan F, Lv Z, et al. A short review of through-silicon via (tsv) interconnects: metrology and analysis. *Applied Sciences.* **2023**;13(14):8301. doi: [10.3390/app13148301](https://doi.org/10.3390/app13148301)

[77] Körögöl Ç, Pop E. High thermal conductivity insulators for thermal management in 3d integrated circuits. *IEDL.* **2023**;44(3):496–499. doi: [10.1109/LED.2023.3240676](https://doi.org/10.1109/LED.2023.3240676)

[78] Wei H, Wu TF, Sekar D, et al. Cooling three-dimensional integrated circuits using power delivery networks. In: *2012 International Electron Devices Meeting*. San Francisco, CA, USA. **2012**. pp. 14.2.1–14.2.4. doi: [10.1109/IEDM.2012.6479040](https://doi.org/10.1109/IEDM.2012.6479040)

[79] Wang KJ, Sun HC, Wang KZ. A micro-channel cooling model for a three-dimensional integrated circuit considering through-silicon vias. *Micro And Nanosystems.* **2021**;13(1):49–54. doi: [10.2174/1876402912666200123154001](https://doi.org/10.2174/1876402912666200123154001)

[80] Huang H, Shan C, Long F, et al. The adoption of novel cooling liquids for enhancing heat transfer performance of three-dimensional integrated circuits with embedded micro-channel. *Thermal Science.* **2024**;29(00):175–175.

[81] Xiang X, Liu W, Fan A. Comparison between the cooling performances of micro-jet impingement systems using liquid metal and water as coolants for high power electronics. *Int J Therm Sci.* **2022**;173:107375. doi: [10.1016/j.ijthermalsci.2021.107375](https://doi.org/10.1016/j.ijthermalsci.2021.107375)

[82] Tiwei T, Oprins H, Cherman V, et al. High efficiency direct liquid jet impingement cooling of high power devices using a 3d-shaped polymer cooler. In: 2017 IEEE International Electron Devices Meeting (IEDM). **2017**. pp. 32.5.1–32.5.4. doi: [10.1109/IEDM.2017.8268487](https://doi.org/10.1109/IEDM.2017.8268487)

[83] Wu CJ, Hsiao ST, Wang JY, et al. Ultra high power cooling solution for 3d-ics. In: 2021 Symposium on VLSI Technology. **2021**;1–2. doi: [10.23919/VLSICircuits52068.2021.9492489](https://doi.org/10.23919/VLSICircuits52068.2021.9492489)

[84] Liu Z, Li Y, Hu J, et al. Deepoheat: operator learning-based ultra-fast thermal simulation in 3d-ic design. In: 2023 60th ACM/IEEE Design Automation Conference (DAC). IEEE; **2023**. pp. 1–6. doi: [10.1109/DAC56929.2023.10247998](https://doi.org/10.1109/DAC56929.2023.10247998)

[85] Wei T, Oprins H, Cherman V, et al. High-efficiency polymer-based direct multi-jet impingement cooling solution for high-power devices. *ITPE.* **2018**;34(7):6601–6612. doi: [10.1109/TPEL.2018.2872904](https://doi.org/10.1109/TPEL.2018.2872904)

[86] Ao L, Ramiere A. Through-chip microchannels for three-dimensional integrated circuits cooling. *Therm Sci Eng Prog.* January **2024**;47:102333. doi: [10.1016/j.tsep.2023.102333](https://doi.org/10.1016/j.tsep.2023.102333)

[87] Rich D, Srimani T, Malakoutian M, et al. Efficient ultra-dense 3d ic power delivery and cooling using 3d thermal scaffolding. In: Proceedings of the 43rd IEEE/ACM International Conference on Computer-Aided Design. **2024**. pp. 1–9. doi: [10.1145/3676536.3676760](https://doi.org/10.1145/3676536.3676760)

[88] Jeon S, Kwak H, Lee W. A study of advancing ultralow-power 3d integrated circuits with tei-lp technology and ai-enhanced pid autotuning. *Mathematics.* **2024**;12(4):543. doi: [10.3390/math12040543](https://doi.org/10.3390/math12040543)

[89] Ballard J, Hubbard M, Jung SJ, et al. Nano-engineered thin-film thermoelectric materials enable practical solid-state refrigeration. *Nat Commun.* **2025**;16(1):4421. doi: [10.1038/s41467-025-59698-y](https://doi.org/10.1038/s41467-025-59698-y)

[90] Zimmer B, Tell SG, Gray CT. A 77 fJ/bit 8 gbps low-latency self-timed die-to-die link for 2.5d and 3d interconnect in 3nm. In: 2025 Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits). **2025**. pp. 1–3. doi: [10.23919/VLSITechnologyandCir65189.2025.11074882](https://doi.org/10.23919/VLSITechnologyandCir65189.2025.11074882)

[91] Nishi Y, Poulton J, Turner W, et al. A 0.297-pJ/bit 50.4-gb/s/wire inverter-based short-reach simultaneous bi-directional transceiver for die-to-die interface in 5-nm cmos. *IEEE J Solid State Circ.* **2023**;58(04):1–12. doi: [10.1109/JSSC.2022.3232024](https://doi.org/10.1109/JSSC.2022.3232024)

[92] Yu DCH, Wang CT, Hsia H. Foundry perspectives on 2.5d/3d integration and roadmap. In: 2021 IEEE International Electron Devices Meeting (IEDM). **2021**. pp. 3.7.1–3.7.4. doi: [10.1109/IEDM19574.2021.9720568](https://doi.org/10.1109/IEDM19574.2021.9720568)

[93] Das S, Riedel S, Naeim M, et al. Bandwidth-latency-thermal co-optimization of interconnect-dominated many-core 3d-ic. *IEEE Trans Very Large Scale Integr VLSI Syst.* **2025**;33(2):346–357. doi: [10.1109/TVLSI.2024.3467148](https://doi.org/10.1109/TVLSI.2024.3467148)

[94] Kim J, Zhu L, Torun HM, et al. A ppa study for heterogeneous 3-d ic options: monolithic, hybrid bonding, and microbumping. *IEEE Trans Very Large Scale Integr VLSI Syst.* **2024**;32(3):401–412. doi: [10.1109/TVLSI.2023.3342734](https://doi.org/10.1109/TVLSI.2023.3342734)

[95] Zhu M, Zhuo Y, Wang C, et al. Performance evaluation and optimization of hbm-enabled gpu for data-intensive applications. In: Design, Automation & Test in Europe Conference & Exhibition (DATE). **2017**. **2017**. pp. 1245–1248.

[96] Peng X, Kaul A, Bakir MS, et al. Heterogeneous 3-d integration of multitier compute-in-memory accelerators: an electrical-thermal co-design. *ITED.* **2021**;68(11):5598–5605. doi: [10.1109/TED.2021.3111857](https://doi.org/10.1109/TED.2021.3111857)

[97] Harb SM, Eisenstadt W. Signal integrity in high speed 3d ic design- a case study. In: 2021 IEEE Nordic Circuits and Systems Conference (NorCAS). **2021**. pp. 1–5. doi: [10.1109/NorCAS53631.2021.9599649](https://doi.org/10.1109/NorCAS53631.2021.9599649)

[98] Cho J, Kim J. Signal integrity design of tsv and interposer in 3d-ic. In: 2013 IEEE 4th Latin American Symposium on Circuits and Systems (LASCAS). **2013**. pp. 1–4. doi: [10.1109/LASCAS.2013.6519092](https://doi.org/10.1109/LASCAS.2013.6519092)

[99] Coakley KJ, Kabos P, Moreau S, et al. Understanding early failure behavior in 3d-interconnects: Empirical modeling of broadband signal losses in tsv-enabled interconnects. *ITED.* **2022**;69(11):1–7. doi: [10.1109/TED.2022.3204936](https://doi.org/10.1109/TED.2022.3204936)

[100] Li M, Periasamy P, Tu KN, et al. Optimized power delivery for 3d ic technology using grind side redistribution layers. In: 2016 IEEE 66th Electronic Components and Technology Conference (ECTC). **2016**. pp. 2449–2454. doi: [10.1109/ECTC.2016.217](https://doi.org/10.1109/ECTC.2016.217)

[101] Sun Y, Jin Y, Cai H, et al. Design, fabrication and measurement of tsv interposer integrated x-band microstrip filter. In: 2019 20th International Conference on Electronic Packaging Technology (ICEPT). **2019**. pp. 1–3. doi: [10.1109/ICEPT47577.2019.245748](https://doi.org/10.1109/ICEPT47577.2019.245748)

[102] Chandrakar S, Gupta D, Majumder MK. Performance analysis of cu/cnt-based tsv: impact on crosstalk and power. *J Comput Electron.* **2022**;21(6):1262–1274. doi: [10.1007/s10825-022-01937-2](https://doi.org/10.1007/s10825-022-01937-2)

[103] Zheng Q, Yang P, Xue H, et al. Research on 3d optical module integrating edge coupler and tsv. *J Lightwave Technol.* **2022**;40(18):6190–6200. doi: [10.1109/JLT.2022.3188362](https://doi.org/10.1109/JLT.2022.3188362)

[104] Jiao B, Qiao J, Jia S, et al. Low stress tsv arrays for high-density interconnection. *Engineering.* **2024**;38:201–208. doi: [10.1016/j.eng.2023.11.023](https://doi.org/10.1016/j.eng.2023.11.023)

[105] Das S, Das DK, Pandit S. Reducing delay and resistance of gnr based interconnect using insertion of buffers. *Analog Integr Circuits Signal Process.* **2025**;123(1):6. doi: [10.1007/s10470-025-02346-8](https://doi.org/10.1007/s10470-025-02346-8)

[106] Mazumdar K, Stan M. Breaking the 3d ic power delivery wall. In: 2012 Conference Record of the Forty Sixth Asilomar Conference on Signals, Systems and Computers (ASILOMAR). **2012**. pp. 741–746. doi: [10.1109/ACSSC.2012.6489111](https://doi.org/10.1109/ACSSC.2012.6489111)

- [107] Fang SH, Lin CT, Liao WH, Huang CC, Chen LC, Chen HM, Lee IH, Kwai DM, Chou YF. On tolerating faults of tsv/microbumps for power delivery networks in 3d ic. In: 2017 IEEE Comput Soc Annu Symp VLSI. 2017;459–464. doi: [10.1109/ISVLSI.2017.86](https://doi.org/10.1109/ISVLSI.2017.86)

- [108] Zhu L, Jo C, Lim SK. Power delivery solutions and ppa impacts in micro-bump and hybrid-bonding 3d ics. IEEE Trans Compon Packag Manuf Technol. 2022;12(12):1969–1982. doi: [10.1109/TCMT.2022.3221025](https://doi.org/10.1109/TCMT.2022.3221025)

- [109] Safari Y, Vaisband B. Integrated power delivery methodology for 3d ics. In: 2022 23rd International Symposium on Quality Electronic Design (ISQED). 2022. pp. 114–119. doi: [10.1109/ISQED54688.2022.9806286](https://doi.org/10.1109/ISQED54688.2022.9806286)

- [110] Sisto G, Chehab B, Gennetret B, et al. Ir-drop analysis of hybrid bonded d-ics with backside power delivery and  $\mu$ - & n- tsvs. In: 2021 IEEE International Interconnect Technology Conference (IITC). 2021. pp. 1–3.

- [111] Naeim M, Biswas D, Dai Y, et al. Iterative layout-aware power, thermal and ir-drop co-optimization: ensuring convergency in 3d-ics. IJEST. 2025;1–1. doi: [10.1109/JETCAS.2025.3591727](https://doi.org/10.1109/JETCAS.2025.3591727)

- [112] Wang H, Wang X, Wang Y, et al. A 660w, 96% efficiency 3d heterogeneously integrated digital dc/dc power module for vertical power delivery. In: 2025 IEEE Applied Power Electronics Conference and Exposition (APEC). 2025. pp. 1544–1550. doi: [10.1109/APEC48143.2025.10977479](https://doi.org/10.1109/APEC48143.2025.10977479)

- [113] Wang J, Duan F, Lv Z, et al. A short review of through-silicon via (TSV) interconnect. Metrology and Analysis. 13(14):8301. doi: [10.3390/app13148301](https://doi.org/10.3390/app13148301)

- [114] Miroslanlou R, Taram M, Shirmohammadi Z, Miremadi S.-G. 3dcam: a low overhead crosstalk avoidance mechanism for TSV-based 3d ICs. 2019. doi: [10.48550/arXiv.1901.00568](https://doi.org/10.48550/arXiv.1901.00568)

- [115] Majumder MK, Kumari A, Kaushik BK, et al. Signal integrity analysis in carbon nanotube based through-silicon via. 2014;2014(1):524107. doi: [10.1155/2014/524107](https://doi.org/10.1155/2014/524107)

- [116] Zhao Z, Li J, Yuan H, et al. Electrical characterization of through-silicon-via-based coaxial line for high-frequency 3d integration (invited paper). 11(20):3417. doi: [10.3390/electronics11203417](https://doi.org/10.3390/electronics11203417)